Ref No.: CEMILAC/5390 / AW / 01 / Directives

Issue - 1.0

15 Feb 2016

# Airworthiness Directive 16/2016

# Complex Electronic Hardware Development and Certification

CENTRE FOR MILITARY AIRWORTHINESS & CERTIFICATION (CEMILAC)

DEFENCE RESEARCH & DEVELOPMENT ORGANIZATION

MINISTRY OF DEFENCE, GOVT OF INDIA

# **Documentation Page**

| Document Classific   | ation: Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                 |  |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Doc. No:             | 16/2016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                 |  |  |  |  |

| Doc. Date: 15 F      | eb 2016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | No. of Pages: 17                                                                                                                |  |  |  |  |

| Doc. Title:          | Airworthiness Directive on Complex Ele<br>Certification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ectronic Hardware Development and                                                                                               |  |  |  |  |

| Key Words:           | Complex Electronic Hardware (CEH), Design Enteron Involvement (SoI), Level of CEMILAC Involvement                                                                                                                                                                                                                                                                                                                                                                                                                                      | mplex Electronic Hardware (CEH), Design Entry, Simulation, Certification, Stage of olvement (SoI), Level of CEMILAC Involvement |  |  |  |  |

| Project No: NA       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                 |  |  |  |  |

|                      | Akin to qualification of hardware, the constituent software and custom micro code components called as Complex Electronic Hardware (CEH) of a system or subsystem needs qualification. Hardware and Software qualification has been well established in the Defence Avionics Industry. Of late, qualification of CEH is gaining importance due to the complexity and volume of algorithms/logic being built into it. CEH includes FPGAs, ASIC PLDs etc. This directive will focus on the development and certification aspects of CEH. |                                                                                                                                 |  |  |  |  |

|                      | ress: CEMILAC, DRDO, Min. of Defence, Marathah                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | alli Colony PO, Bangalore 37                                                                                                    |  |  |  |  |

| Distribution List: ( | Concerned DRDO Labs, PSUs, DGAQA and Users                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                 |  |  |  |  |

| Prepared By:         | Systems Group, CEMILAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                 |  |  |  |  |

| cpaica by.           | Systems Group, CENTERC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                 |  |  |  |  |

| Feedback From:       | Concerned DRDO Labs, PSUs, DGAQA and U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Jsers                                                                                                                           |  |  |  |  |

| Feedback From:       | Concerned DRDO Labs, PSUs, DGAQA and U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Jsers J                                                                                                                         |  |  |  |  |

|                      | Concerned DRDO Labs, PSUs, DGAQA and U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                 |  |  |  |  |

| Feedback From:       | Concerned DRDO Labs, PSUs, DGAQA and U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | yapal<br>(Airworthiness)                                                                                                        |  |  |  |  |

| Feedback From:       | Concerned DRDO Labs, PSUs, DGAQA and U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | yapal                                                                                                                           |  |  |  |  |

# **Revision History**

| Document Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | : Complex Electronic | Hardware Developr | nent and Certification |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|------------------------|--|--|--|

| Document Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | : 16/2016            |                   |                        |  |  |  |

| Revision Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Date                 | Approval          | Remarks                |  |  |  |

| Issue - 0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14 Dec 2015          |                   | Draft for Review       |  |  |  |

| Issue - 0.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 08 Jan 2016          |                   | Comments incorporated  |  |  |  |

| Issue - 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15 Feb 2016          | CE(A)             | Final                  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                   |                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                   |                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                   |                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                   |                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                   |                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                   |                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                   |                        |  |  |  |

| 2770.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                   |                        |  |  |  |

| - dust                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                   |                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                   |                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                   |                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                   |                        |  |  |  |

| Marie Company |                      |                   |                        |  |  |  |

# **Contents**

| T |      |       | of Contents                                  |            |

|---|------|-------|----------------------------------------------|------------|

| 1 | In   |       | duction                                      |            |

|   | 1.1  |       | Purpose                                      | 5          |

|   | 1.2  |       | Scope                                        | 5          |

|   | 1.3  |       | Applicability                                | 5          |

|   | 1.4  |       | References                                   | 5          |

|   | 1.5  |       | Acronyms                                     | 5          |

| 2 | С    | ΈН    | Life Cycle                                   | 7          |

|   | 2.1  |       | Simple Electronic Hardware (SEH)             | 7          |

|   | 2.2  |       | Complex Electronic Hardware (CEH)            | 7          |

|   | 2.3  |       | Hardware Item                                | 7          |

|   | 2.4  |       | Safety Assessment (SA)                       | 7          |

|   | 2.5  |       | Independent Verification & Validation (IV&V) | 7          |

|   | 2.6  |       | CEH Life Cycle Activities                    | 7          |

|   | 2    | 2.6.3 | l Planning Phase                             | 8          |

|   | 2    | 2.6.2 | Development Phase                            | 9          |

|   | 2    | 2.6.3 | Supporting Processes                         | .2         |

| 3 | c    | Cert  | ification Aspects for CEH                    | .3         |

|   | 3.1  |       | CEH Certification                            | .3         |

|   | 3.2  |       | Stages of Involvement (SOI)                  | .3         |

|   | 3.3  |       | Level of CEMILAC Involvement                 | 4          |

| 4 | . 4  | ٩dd   | itional considerations                       | 15         |

|   | 4.1  |       | COTS and IP Cores                            | L5         |

|   | 4.2  |       | Change in CEH                                | L5         |

|   | 4.3  |       | Tool Qualification                           | L5         |

| 5 | , F  | Pro   | mulgation                                    | <b>L</b> 6 |

|   | 5.1  |       | Promulgation                                 | 16         |

|   | 5.2  | 2     | Feedback                                     | 16         |

| ļ | Appe | ndi   | x 'A' - Feedback Form                        | 17         |

#### 1 Introduction

# 1.1 Purpose

Airborne Electronics systems are presently designed widely with Complex Electronic Hardware (CEH) like Field Programmable Gate Arrays (FPGAs), Application Specific Integrated Circuits (ASICs) and other Programmable Logic Devices (PLDs). In Indian military avionics also, the trend of using CEH has increased. Even currently, many of the processor based applications are getting replaced with CEH. Almost all the electronics is bound to have CEH because of its flexible / reliable programming that can be obtained when compared to processor based software.

The use of CEH for safety and mission critical aircraft applications are posing new safety and certification challenges. These challenges arise from the concern that, implementation of aircraft functions in CEH is vulnerable to the adverse effects of hardware design errors. To alleviate this risk, it has become necessary to ensure that hardware design is addressed in a more consistent and verifiable manner during both the design and certification processes.

Hence, it becomes necessary to formulate a directive for Development and Certification of CEH in the Indian military airborne applications.

# 1.2 Scope

The Scope of this directive is to address the major activities and artefacts involved in Design, Development and Certification of Complex Electronic Hardware (CEH) for Indian Military airborne applications.

# 1.3 Applicability

This directive is applicable from the date of release.

# 1.4 References

- a. Procedure for Design, Development and Production of Military Aircraft and Airborne Stores DDPMAS 2002 and DDPMAS-2002, Vol-II, Software Development and Certification.

- DO-254, Design Assurance Guidance for Airborne Electronic Hardware, published by RTCA, Inc., 2000

- c. FAA Order 8110.105 CHG 1,Simple And Complex Electronic Hardware Approval Guidance, 2008

- d. SAE/ARP 4761, (Aerospace Recommended Practice 4761A) Guidelines and methods for conducting the safety assessment process on civil airborne systems and equipment, 1996-12

#### 1.5 Acronyms

| i.    | CDD Conceptual Design Data |                                           |  |

|-------|----------------------------|-------------------------------------------|--|

| ii.   | DDD                        | Detail Design Data                        |  |

| iii.  | HAS                        | Hardware Accomplishment Summary           |  |

| iv.   | HATC                       | Hardware Acceptance Test Criteria         |  |

| v.    | HCI                        | Hardware Configuration Index              |  |

| vi.   | НСМР                       | Hardware Configuration Management Plan    |  |

| vii.  | HCMR                       | Hardware Configuration Management Records |  |

| viii. | HCS                        | Hardware Coding Standard                  |  |

| ix.    | HDL  | Hardware Description Language                  |        |

|--------|------|------------------------------------------------|--------|

| x.     | HDP  | Hardware Development Plan                      |        |

| xi.    | HDS  | Hardware Design Standard                       |        |

| xii.   | HECI | Hardware Environment Configuration Index       |        |

| xiii.  | HPAP | Hardware Process Assurance Plan                |        |

| xiv.   | HPAR | Hardware Process Assurance Records             |        |

| XV.    | HRAP | Hardware Reviews and Analysis Procedures       |        |

| xvi.   | HRAR | Hardware Reviews and Analysis Results          |        |

| xvii.  | HRD  | Hardware Requirements Data                     |        |

| xviii. | HRS  | Hardware Requirement Standard                  |        |

| xix.   | HTD  | Hardware Traceability Data                     |        |

| xx.    | HTP  | Hardware Test Plan                             |        |

| xxi.   | HTR  | Hardware Test Results                          |        |

| xxii.  | HVVP | Hardware Verification and Validation Plan      |        |

| xxiii. | HVVS | Hardware Verification and Validation Standards |        |

| xxiv.  | IRD  | Interface Requirements Data                    |        |

| xxv.   | PHAC | Plan for Hardware Aspects of Certification     |        |

| xxvi.  | PR   | Problem Reports                                |        |

| xxvii. | RTL  | Register Transfer Level                        | 265555 |

| xviii. | SSA  | System Safety Assessment                       |        |

| xxix.  | TAQD | Tool Assessment and Qualification Data         |        |

# 2 CEH Life Cycle

# 2.1 Simple Electronic Hardware (SEH)

A hardware item is considered simple if a comprehensive combination of deterministic tests and analyses appropriate to the Design Assurance Level (DAL) can ensure correct and complete functional performance under all foreseeable operating conditions, with no anomalous behaviour.

# 2.2 Complex Electronic Hardware (CEH)

A hardware item that is not simple is considered to be 'complex'. System design team shall classify a given hardware item into SEH/CEH early in project.

#### 2.3 Hardware Item

For this directive, a hardware item is defined as any custom micro coded component that is programmed by the developer. Hardware item includes, but not limited to FPGAs, ASICs, PLDs, PALs. It also covers those similar electronic components used in the design of aircraft systems and equipment.

# 2.4 Safety Assessment (SA)

System Engineering Process shall identify and allocate system requirements to be implemented through CEH. Safety Assessment Process shall be followed to determine the Design Assurance Level for CEH. ARP 4761 or MIL-STD-882 can be used for Safety Assessment (SA) Process.

### 2.5 Independent Verification & Validation (IV&V)

IV&V is a team of people from system experts, designer's IV&V team, CEMILAC, DGAQA and user representative. The constitution of the IV&V team for review of the artefacts at different phases will be addressed in PHAC and HVVP documents.

# 2.6 CEH Life Cycle Activities

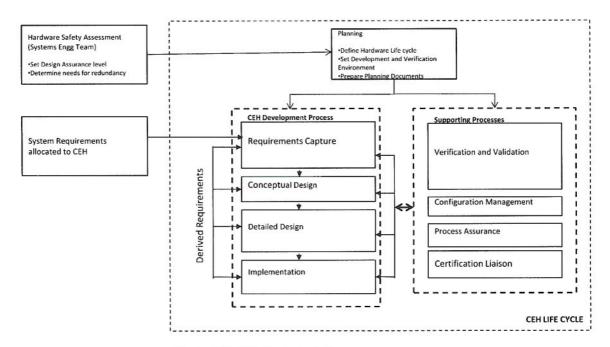

CEH lifecycle activities are shown in Fig 1. CEH Life cycle begins with the allocation of System requirements to CEH. There is a continuous flow of information from CEH life cycle to System Engineering process like fault containment boundaries/ failure recovery, CEH verification activities to be performed at system level etc. The CEH life cycle includes Planning Process, Hardware Design Process and Supporting Processes. Planning process involves planning for hardware aspects of certification and related other plans. Hardware Design Process includes activities like Requirements capture, Conceptual and Detailed Design, and Implementation. Conceptual Design and Detailed Design may be merged into one for less complicated programs and appropriately documented in the Plans. The CEH will be programmed as per approved hardware configuration, during production process. Supporting Processes provide umbrella activities covering the whole CEH life cycle span. Model based Design and development is not addressed in the life cycle process described in this document.

Fig 1. CEH: Life Cycle Activities

# 2.6.1 Planning Phase

Planning phase describes the CEH planning process which is used to control the development of the CEH item. This process produces the hardware plans, which may be contained in one or more documents. Standard documents covering specific hardware design life cycle processes, such as configuration management or process assurance, are acceptable provided they meet the planning objectives for the applicable process.

The planning process establishes the various hardware plans, standards, procedures, activities, methods, and tools required to develop, verify and maintain the hardware life cycle data.

# **Documents and Process for Planning Phase:**

| Supplier of<br>Inputs                     | Inputs                                                                                  | Process                                                                               | Output of the<br>Process                                                               | Users of the outputs           |

|-------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------|

| System Engineer HW Designer /CEH Designer | -Technical/ Functional<br>Specification of the LRU<br>allocated to CEH<br>-SSA document | Preparation of planning documents  Identifying the criticality level allocated to CEH | PHAC HCMP HVVP, HPAP HDP HRS, HDS, HVVS, HCS Tool Qual Assessment data (if applicable) | CEMILAC, QA,<br>IV&V,<br>DGAQA |

# Verification of the Planning Phase:

| Supplier<br>Inputs | of  | Inputs                             | Process                     | Output of the<br>Process            | Stage of<br>Involvement |

|--------------------|-----|------------------------------------|-----------------------------|-------------------------------------|-------------------------|

| HW/<br>Designer    | RTL | All previous outputs in this phase | Review by IV&V, Audit by QA | Inputs Base-<br>lined<br>HRAR, HPAR | Sol-1                   |

Note: In this phase, Hardware Traceability Data (HTD) to be made w.r.t. all the outputs and inputs.

# 2.6.2 Development Phase

# 2.6.2.1 Requirements Capture

The Requirement process establishes the requirements of CEH to produce the hardware life cycle data. Requirements are identified, defined and documented. The requirements specify the functional, performance, safety, quality, maintainability, and reliability requirements for the hardware item being developed. During this phase, the activities of the designer and verification engineer are given below along with the necessary outputs. Review activity of the same phase is also given.

# **Documents and Process for Requirement Phase:**

| Supplier of<br>Inputs    | Inputs                                                                                  | Process                                                                                                       | Output of the<br>Process | Users of the outputs |

|--------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------|----------------------|

| HW/CEH                   | All Plans and HRS                                                                       | Developing detailed functional                                                                                | HRD                      | CEMILAC, QA,         |

| Designer                 | -Technical/ Functional<br>Specification of the LRU<br>allocated to CEH<br>-SSA document | requirements allocated to CEH by<br>the HW/CEH designer<br>Developing Redundancy<br>Requirements based on SSA | IRD                      | IV&V,<br>DGAQA       |

| Verification<br>Engineer |                                                                                         | Developing behavioural specifications for testing of CEH                                                      | HTP (HL),<br>HRAP        |                      |

# Verification of the Requirement phase:

| Supplier of Inputs            | Inputs                             | Process                     | Output of the<br>Process                       | Stage of<br>Involvement |

|-------------------------------|------------------------------------|-----------------------------|------------------------------------------------|-------------------------|

| Designer/Verification<br>Engr | All previous outputs in this phase | Review by IV&V, Audit by QA | Baselined HRD, IRD, HTP (HL), HRAP, HRAR, HPAR | Sol-2                   |

Note: In this phase, Hardware Traceability Data (HTD) to be made w.r.t. all the outputs and inputs.

## 2.6.2.2 Conceptual Design

Architectural design of the CEH to be brought out in Conceptual design phase. During this phase, the activities of the designer and verification engineer are given below along with the necessary documents. Review activity of the same phase is also given.

# Documents and Process for Conceptual Design Phase:

| Supplier of<br>Inputs | Inputs          | Process                                                                | Output of the<br>Process                                      | Users of the outputs                      |

|-----------------------|-----------------|------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------|

| CEH Designer          | HRD<br>IRD, HDS | High Level Architecture/ Block representation at component (CEH) level | High Level<br>Arch/Block<br>diagram at<br>CEH level (<br>CDD) | Designer,<br>CEMILAC, QA<br>IV&V<br>DGAQA |

| Verification<br>Engr  | CDD, HVVS       | Deriving Test Bench Architecture diagram for CEH                       | Test Bench<br>Arch Diag                                       |                                           |

# Verification of the Conceptual Design phase:

| Supplier of Inputs            | Inputs                                 | Process        | Output of the<br>Process                                  | Stage of<br>Involvement |

|-------------------------------|----------------------------------------|----------------|-----------------------------------------------------------|-------------------------|

| Designer/Verification<br>Engr | All the previous outputs in this phase | Review by IV&V | Baselined<br>CDD, Test<br>bench Arch<br>Blk Diag,<br>HRAR | Sol-2                   |

Note: In this phase, Hardware Traceability Data (HTD) to be made w.r.t. all the outputs and inputs.

# 2.6.2.3 Detailed Design:

The Design process establishes the design of CEH to produce the hardware life cycle data. The detailed design process produces detailed design data using the hardware item requirements as the basis for the detailed design. During this phase, the activities of the designer and verification engineer are given below along with the necessary documents. Review activity of the same phase is also given.

# **Documents and Process for Detailed Design Phase:**

| Supplier of<br>Inputs    | Inputs                                      | Process                                                              | Output of the<br>Process                                  | Consumer of<br>the outputs                |

|--------------------------|---------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------|

| CEH Designer             | CDD, HDS                                    | Converting CEH requirements (HRD/IRD) & CDD into lower level modules | Module level<br>Schematics &<br>Block<br>diagrams,<br>DDD | Designer,<br>CEMILAC, QA<br>IV&V<br>DGAQA |

| Verification<br>Engineer | Test Bench Arch Block<br>Diagram, DDD, HVVS | Deriving Test procedures for CEH (Test benches)                      | HTP (LL)                                                  |                                           |

# Verification of the Detailed Design phase:

| Supplier of<br>Inputs | Inputs                  | Process                      | Output of the<br>Process | Stage of<br>Involvement |

|-----------------------|-------------------------|------------------------------|--------------------------|-------------------------|

| Designer              | All previous outputs in | Review by a committee, IV&V, | Baselined                | Sol-2                   |

| •                     | this phase              | Audit by QA                  | DDD, HTP (LL),           |                         |

|                       |                         |                              | HRAR, HPAR               |                         |

Note: In this phase, Hardware Traceability Data (HTD) to be made w.r.t. all the outputs and inputs.

# 2.6.2.4 Implementation Phase

The implementation process converts the design of CEH to produce the bit stream (Net list) to be incorporated into the CEH. During this phase, the activities of the designer and IV&V are given below along with the necessary documents. Review activity of the same phase is also given.

# **Documents and Process for Implementation Phase:**

| Supplier of<br>Inputs | Inputs                | Process                                                            | Output of the<br>Process                       | Users of the<br>outputs                   |

|-----------------------|-----------------------|--------------------------------------------------------------------|------------------------------------------------|-------------------------------------------|

| CEH Designer          | HRD, CDD, DDD,<br>HCS | Develop RTL/HDL code, Synthesis, P&R, define and apply constraints | HDL/RTL code,<br>Netlist, Synthesis<br>Reports | Designer,<br>CEMILAC, QA<br>IV&V<br>DGAQA |

Verification of the implementation phase: (IV&V team)

| Supplier of<br>Inputs | Inputs                             | Process                                                                                           | Output of the<br>Process | Stage of<br>Involvement |

|-----------------------|------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------|-------------------------|

| Designer              | All previous outputs in this phase | Verification of Net list, code review etc. Implementation of all the requirements to be verified. | HRAR, HPAR               | Sol-3                   |

Note: In this phase, Hardware Traceability Data (HTD) to be made w.r.t. all the outputs and inputs.

# 2.6.2.5 Testing Phase

The testing process involves the following activities and documents during testing and its verification stage. Following the CEH testing activity, integration of hardware, software and CEH be taken up during integration testing for combined and integrated checks.

# **Documents and Process for Testing Phase:**

| Verification | HTP (HL/LL) | Developing models and writing test     | HRAR, HTR,       | Designer, |    |

|--------------|-------------|----------------------------------------|------------------|-----------|----|

| Engineer     | HCS         | benches /test cases, Perform top level | Functional /Gate | CEMILAC,  | QA |

| N-10         |             | and module level verification by:      | level simulation | IV&V      |    |

|              |             | Behavioural/functional and timing      | reports, Code    | DGAQA     |    |

|              |             | simulation, Coverage Testing, FPGA     | Coverage         |           |    |

|              |             | Timing analysis, In Time/On Target     | reports etc.     |           |    |

|              |             | Testing, Integration testing at        | 500              |           |    |

|              |             | Board/LRU level etc.                   |                  |           |    |

|              |             |                                        |                  |           |    |

Verification of the Testing phase: (IV&V team)

| Supplier of<br>Inputs | Inputs                  | Process                      |     | Output of the<br>Process | Stage of<br>Involvement |

|-----------------------|-------------------------|------------------------------|-----|--------------------------|-------------------------|

| Verification          | All previous outputs in | Implementation of all        | the | HRAR, HTR                | Sol-3                   |

| Engineer & Designer   | this phase              | requirements to be verified. |     | (HL/LL), HPAR            |                         |

Note: In this phase, Hardware Traceability Data (HTD) to be made w.r.t. all the outputs and inputs.

# 2.6.3 Supporting Processes

- 2.6.3.1 Verification and Validation: Verification and Validation shall be done as per HVVP. The role of a verification engineer during each phase of CEH life cycle has been discussed above.

- 2.6.3.2 Configuration Management: The configuration management process is intended to provide the ability to consistently replicate the configuration item, regenerate the information if necessary and modify the configuration item in a controlled fashion if modification is necessary. Configuration Management shall be done as per HCMP.

- 2.6.3.3 Process Assurance: Process assurance ensures that the life cycle process objectives are met and activities have been completed as outlined in plans or that deviations have been addressed. There is no intent to impose specific organizational structures.

Process assurance activities shall be achieved with independence in order to objectively assess the life cycle process, identify deviations and ensure corrective action. Process assurance shall be done as per HPAP.

2.6.3.4 Certification Liaison: Certification liaison defines the communication between the system developer and the certification authority, covering how data is approved, joint reviews, and when and how the certifying authority witnesses compliance testing. Certification liaison shall be as per PHAC.

### **Documents for Certification Completion:**

| Supplier of<br>Inputs | Inputs                                                         | Process                                                                                       | Output of the<br>Process  | Stage of<br>Involvement |

|-----------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------|-------------------------|

| Applicant             | All the baseline<br>documents<br>HCI, HECI, HCMR, HPAR,<br>HAS | Final review of the accomplishments and verification activities of the development lifecycle. | Approved HCI,<br>HECI,HAS | Sol-4                   |

# 3 Certification Aspects for CEH

# 3.1 CEH Certification

Certification follows concurrent approach where certification agency will be involved in the complete life cycle of CEH. Each System/LRU shall have a Route to Certification (RTC) document from which PHAC shall be derived during Planning Phase. Stage of Involvement (SOI) and Level of Involvement (LOFI) of Certification agency are documented during the planning process. On satisfactory completion of development and other activities as planned, the CEH item will be certified for use in the airborne electronic hardware.

# 3.2 Stages of Involvement (SOI)

| Life Cycle Phases        | Certification Activities                                        |  |  |

|--------------------------|-----------------------------------------------------------------|--|--|

| Planning                 | Hardware Planning<br>Review (Sol-1)                             |  |  |

| Requirements             | Hardware                                                        |  |  |

| Conceptual Design        | Development<br>Review (Sol – 2)                                 |  |  |

| Detailed Design          | Review (301 - 2)                                                |  |  |